# **Dielectric engineering**

Characterization, development and process damage minimization of various silicon oxides

Jan Germain Gabriel Ackaert

ISBN: 90-365-2069-x

## **DIELECTRIC ENGINEERING**

# CHARACTERIZATION, DEVELOPMENT AND PROCESS DAMAGE MINIMIZATION OF VARIOUS SILICON OXIDES

#### DISSERTATION

to obtain

the doctor's degree at the University of Twente,

on the authority of the rector magnificus,

prof.dr. F.A. van Vught,

on the account of the decision of the graduation committee,

to be publicly defended

on Wednesday 8th of September 2004 at 15.00

by

Jan Germain Gabriel Ackaert

born on 31st of December 1958

in Kortrijk, Belgium

Dit proefschrift is goedgekeurd door de promotor prof.dr.ir. F.G Kuper

'.... doe nou maar wat je zegt, dat is al moeilijk genoeg ....' naar Bram Faas

Aan Jonas, Katrijn, Karel en Hilde voor de vele uren dat papa weer zat te 'tikken' en mijn ouders voor hun nooit aflatende steun

#### De promotiecommissie:

Voorzitter:

Prof.dr. W.H. Zijm Universiteit Twente, EWI

Secretaris:

Prof.dr. W.H. Zijm Universiteit Twente, EWI

**Promotor:**

Prof.dr.ir. F.G. Kuper Universiteit Twente / Philips Semiconductors

Referent:

Dr. A. Scarpa Philips Semiconductors Nijmegen

Leden:

Prof.dr. J. Schmitz Universiteit Twente, EWI

Prof.dr.ir. A.J. Mouthaan Universiteit Twente, EWI

Prof.dr.ir. G. Groeseneken KU Leuven

## Levensloop

Jan Ackaert werd op 31 december 1958 geboren te Kortrijk in de Belgische provincie West-Vlaanderen. Hij behaalde in 1976 zijn Humaniora diploma aan het Onze-Lieve-Vrouwe College te Oostende. Hierna studeerde hij Chemie aan de Industriële Hogeschool te Oostende waar hij afstudeerde in de richting Biochemie op de gaschromatografische bepaling van aminozuren in serum. Het ingenieurs diploma werd in 1980 'met lof' behaald. Hij vervulde zijn militaire dienst waarna hij in 1982 in dienst trad bij Centraal Laboratorium UCB te Oostende. In 1983 trad hij in dienst bij Bayer te Brugge als verantwoordelijke voor het analytisch laboratorium en milieu. Sinds 1988 werkt hij bij de halfgeleider fabrikant AMIS te Oudenaarde. Na een aantal jaren als proces support ingenieur in de dunne films en implant afdeling actief te zijn geweest werd hij in 1994 aangesteld als proces module ontwikkeling ingenieur. Hier werkte hij aan de ontwikkeling van diverse proces modules: metallisatie, intermetaal diëlectrica, planarisatie, pre-epi proces voor bipolaire en hoogspannings technologiëen, diëlectrica als basis voor selectieve epi depositie, diëlectrica voor metaal-metaal capaciteiten, tunnel en interpoly oxides in geheugen cellen. Als rode draad door de ontwikkeling van de proces modules was er de impact van de effecten van het plasma tijdens het fabriceren van de halfgeleider. Over deze materie werden dan ook vele publicaties gemaakt onder andere in Solid State Electronics, Journal Microelectronics Reliability en IEEE Transactions on Electron Devices en op de conferenties P2ID, ESSDERC, ESPID, IPFA, ESREF en ICICDT. Hij werd uitgenodigd als conference committee member voor de ICICDT conferentie bij de werkgroepen plasma damage and advanced memory devices.

## **Biography**

Jan Ackaert was born in Kortrijk, Belgium in 1958. He received the M.S. degree in Chemistry 'with honor' from Ostend Industrial High School in 1980 with a specialization in biochemistry. After one year with the central laboratory of UCB in Ostend, he joined Bayer as the manager or the analytical laboratory and environment. In 1988 he joined AMIS in Oudenaarde as process support engineer. In 1992 he became process module development engineer covering various process modules as metal interconnects, inter metal dielectrics, buried layers for bipolar and high voltage technologies, dielectrics for selective epi depostion, the dielectrics for metal-metal capacitors, tunnel and interpoly dielectrics for memory cells. As a constant through the development of the process modules, there was interest for the effects of the plasma processes on the devices during the manufacturing of the semiconductor. In this field many publications are made among others in Solid State Electronics, Journal Microelectronics Reliability and the IEEE Transactions on Electron Devices, and on the conferences P2ID, ESSDERC, ESPID, IPFA, ESREF and ICICDT. He is invited as conference committee member of the ICICDT conference with the workgroups plasma damage and advanced memory devices.

#### **Dankwoord**

Vele mensen hebben de afgelopen jaren bijgedragen aan de totstandkoming van de artikelen die in dit proefschrift bijeengebracht zijn. Als eerste dank ik hierbij mijn collega's van de Proces Module Development Group van AMIS:. Ze hebben mij geassisteerd en gestimuleerd mijn eerste wetenschappelijke publicaties te maken, met name Sylvie Boonen, Paul Colson, Peter Coppens, Malik Fatkhoudinov en Hocine Ziad (in alfabetische volgorde). Heel erg belangrijk en gewaardeerd hierbij zijn het management van Eddy De Backer en de directie van Marnix Tack. In deze groep heb ik geleerd dat werken best met veel plezier te combineren valt waar de genoemde groepsleden veel aan bijgedragen hebben.

In Oudenaarde is het werk klimaat in technology research en development groep en de nauwe samenwerking met de process support engineers in de waferfab en de designers, device fysici en product engineers een uitstekende voedingsbodem: Een ruime keuze aan interessante en relevante onderwerpen, voldoende middelen om deze gedegen uit te zoeken, goede discussie partners en altijd een plezierige en positieve samenwerking, ook als het business belang grote druk op de groep legde. Onmisbare bijdragen, zowel in materiele als immateriële zin, zijn echter ook geleverd door de vele TRD collega's. Hierbij wil ik in het bijzonder Klara en Antony danken voor het zeer nauwgezette nalezen van dit werk.

Belangrijke steun kwam tevens vanuit IMEC. Hierbij niet te vergeten (en hierbij besef ik dat deze lijst steeds onvolledig zal zijn) zijn de bijdragen van Guido Groeseneken, Ludo van de Bempt, Geert van den Bosch, Martin Creusen, Wade Zawalsky, Jan Van Houdt, Robin Degraeve, Luc Haspeslagh, Paul Hendrickx en nog zo veel meer hoogstaande wetenschappers. Een zeer bijzonder en welgemeend woord van dank wil ik richten aan Zhichun Wang. Tijdens haar stage periode op ons bedrijf raakte de studie van plasmaschade in een echte stroomversnelling. Talrijk waren onze uitvoerige, kritische en vruchtbare discussies. In vele van de publicaties, opgenomen in dit werk, heeft zij persoonlijk een zeer belangrijke bijdrage geleverd. Hierbij wil ik ook Cora Salm niet vergeten die de eerste contacten legde tussen AMIS en UT.

De grote inspiratoren van dit proefschrift mogen ook apart geëerd worden: Fred Kuper, mijn promotor en Jurriaan Schmitz. Zonder hun stimulans en vertrouwen in mij was het waarschijnlijk nooit zover gekomen. Fred en Jurriaan, hiervoor hartelijk dank evenals voor het grote geduld dat je ten toon gespreid hebt bij de voltooiing van dit proefschrift.

Verder natuurlijk dank aan Jonas, Katrijn, Karel en Hilde, voor hun grote geduld tijdens al die uren dat 'Papa weer een verhaal aan het schrijven was' en waarbij ze de PC niet zelf konden gebruiken.

Tenslotte wil ik nog mijn ouders vermelden die het studeren en het tot stand komen van dit werk altijd door dik en dun gesteund en aangemoedigd hebben, 'Pa en Ma', bedankt!

#### **Abstract**

Over the various chapters, this thesis describes the characterization and development of a number of applications of silicon dioxides. An oxynitride is developed allowing a much higher SiGe epitaxial deposition rate in a bipolar process. Also a tunneloxide for non volatile memory application is developed and characterized. Once the oxide has been formed and defined it is exposed to the sometimes harsh environments during the following processing steps. Possible process damage due to this exposure is characterized, evaluation methods are developed, process steps are engineered for damage reduction and protection methods are developed.

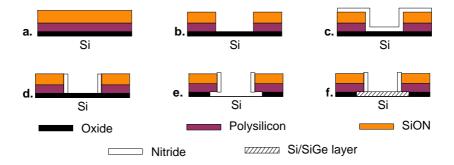

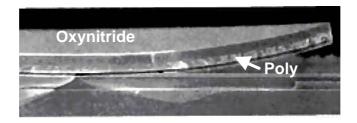

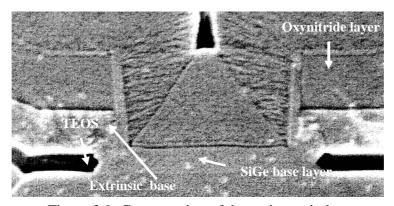

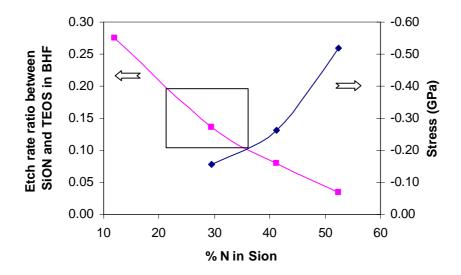

Chapter 2 describes the use of a PECVD oxynitride layer instead of the nitride layer to allow a much higher deposition rate of the selective epitaxial in the heterojunction bipolar transistor interpoly dielectric layer module of a SiGe BiCMOS technology. The composition of the oxynitride layer was chosen as a function of selectivity, etch rate ratio and stress. This layer allows a significant improvement of growth rate of the selective epitaxial deposition by a factor 4 to 5. Good electrical performance and yield have been proven.

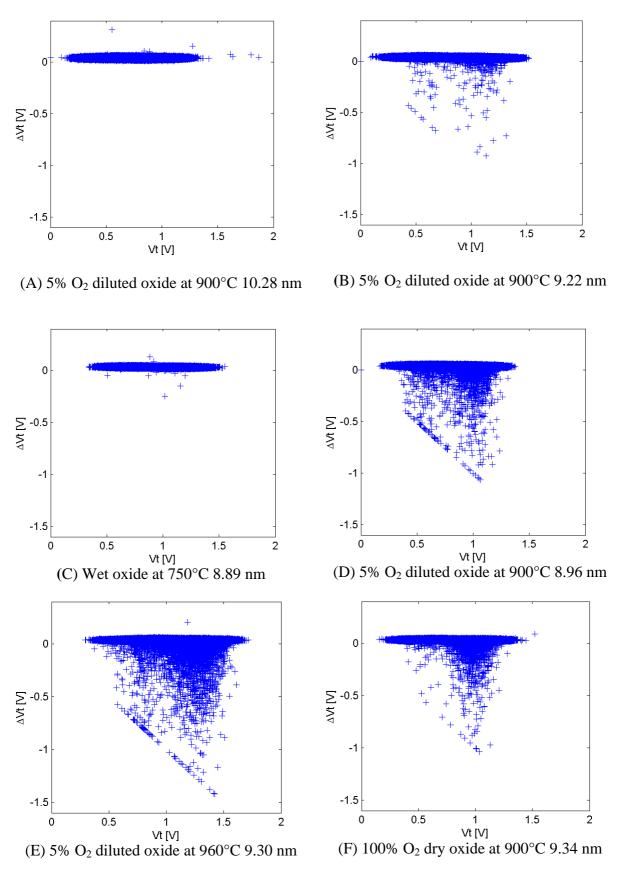

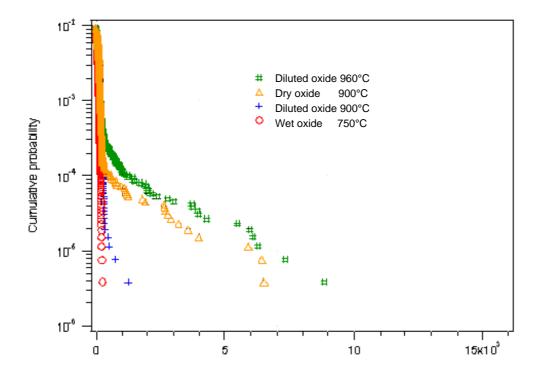

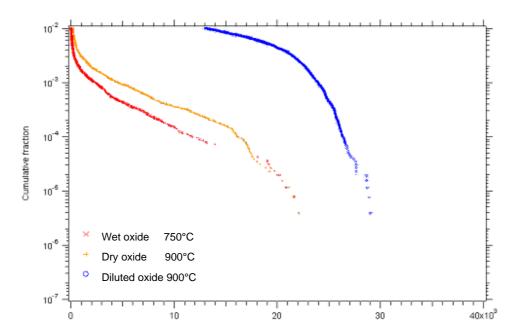

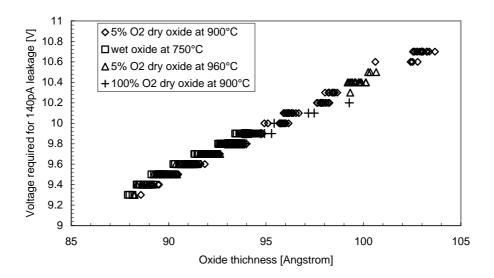

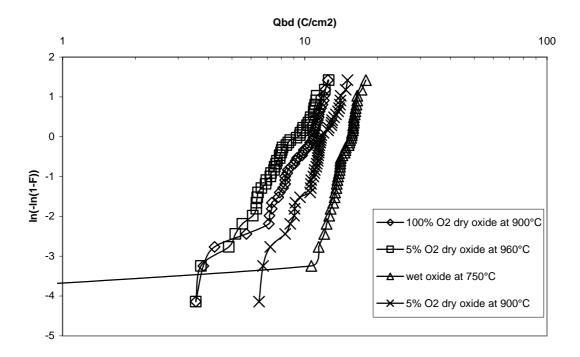

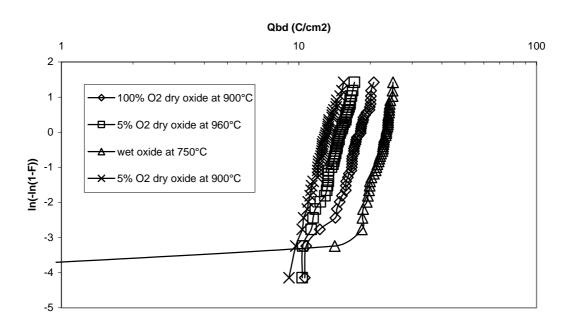

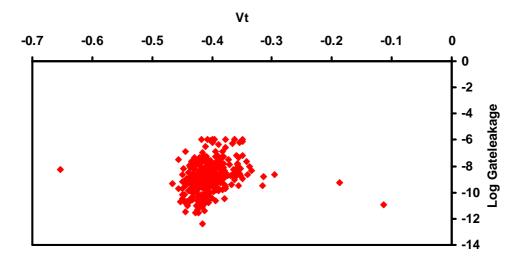

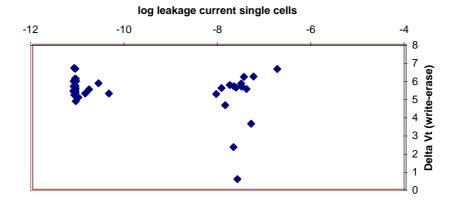

A principal problem of floating gate based non-volatile memories such as flash memories or EEPROMs is anomalous charge loss which leads to threshold voltage ( $V_t$ ) shifts on a time scale of months or years at room temperature. In chapter 3 we compare different types of tunnel oxides and determine the impact on the moving bit issue with different measurement techniques. It is demonstrated that a fast  $Q_{BD}$  test of the channel tunnel oxide is generating exactly the same qualitative ranking as the moving bit test of virgin devices and the  $Q_{BD}$  test of the erase junction tunnel oxide is a measure for the moving bit behaviour of cycled devices. The superior behaviour of the wet oxides in terms of moving bits remains over the full life cycle of the memory cell.

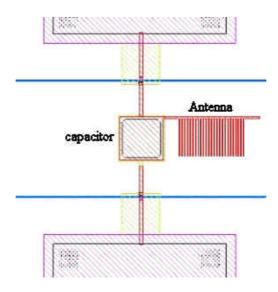

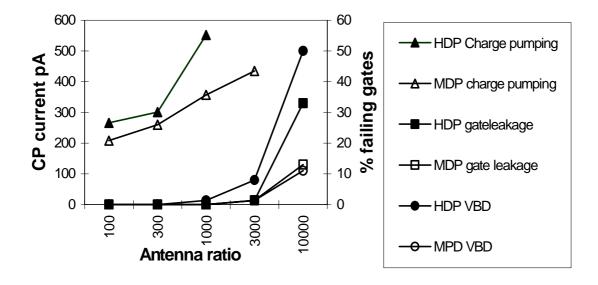

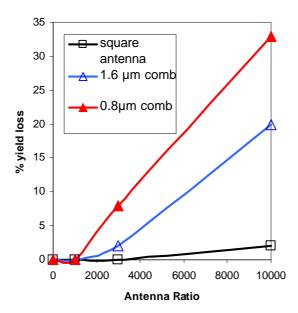

These delicate dielectrics are easily damaged during the further processing of the device. Plasma processing is a major source of process induced damage. To evaluate plasma process induced damage induced by the different process modules on gate oxides and metal-insulator-metal capacitors, test structures with large antennas connected to the gate electrode have been developed. Chapter 4 is describing the test structures required for evaluation of plasma damage on MOS and metal-insulator-metal capacitors and HIMOS<sup>TM</sup> flash memory cells devices. In the majority of cases however, protection structures need to be foreseen already in the design phase of the circuit. This chapter is providing designer guidelines, possible scenarios and required limitations for protecting semiconductor devices against plasma damage. Gate leakage measurements proved to be the most simple, fast and sensitive method.

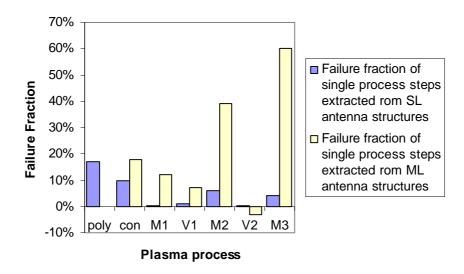

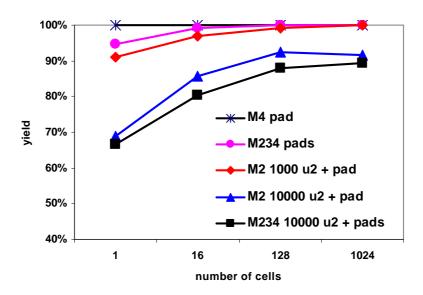

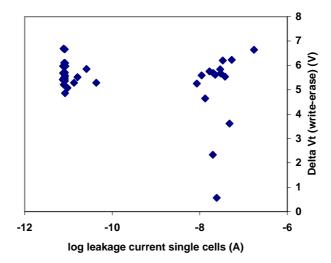

In chapter 5 electron shading effects are discussed as a function of reactor- and transistor-type. Also a new method is proposed to study plasma process-induced latent damage on gate oxide, by using single-layer antenna and multi-layer antenna structures. With this method one can study the plasma process induced damage without suffering from artefacts induced by traditional constant current stress method. It is demonstrated that also the performance of non volatile memory cells are affected by plasma damage. For these cases the suitable protective devices and connection schemes have been developed. The correlation found between low levels of gate leakage and both HC degradation and oxide breakdown is described. This proves that plasma damage affects not only yield but also reliability and device lifetime.

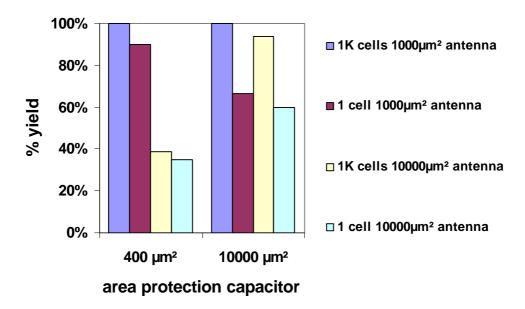

Chapter 6 demonstrates that not only thin gate oxide but also dielectricums thicker than 20nm as used in metal-insulator-metal capacitors are affected by plasma damage. Also for these cases the suitable protective devices and connection schemes have been developed. Evidence is demonstrated that even after the deposition of a thick insulating inter metal dielectric over semiconductor devices, there is still an eminent risk for charging induced damage of gate oxides.

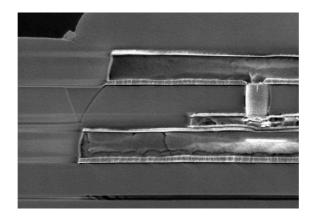

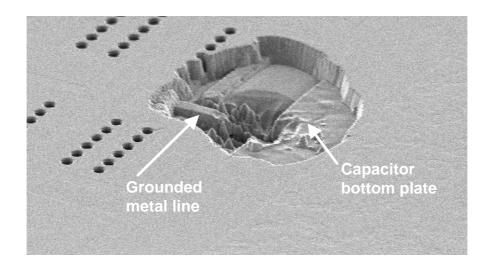

Chapter 7 describes how after a step-by-step investigation of a conventional 5 metal layer CMOS process, a number of plasma damage inducing process steps have been identified and eliminated. During the investigation also a severe case of damage to metal capacitors was discovered. It was found that ESD like discharges are causing severe defects on the metal-insulator—metal capacitors during the post processing of the devices.

### **Samenvatting**

Dit proefschrift behandelt de ontwikkeling en de karakterisatie van een aantal toepassingen van siliciumdioxide in de halfgeleiderindustrie. Een oxynitride werd ontwikkeld dat toelaat om SiGe met een veel hogere snelheid selectief te deponeren in een hetrojunctie bipolaire technologie. Ook werd een tunneloxide in niet-vluchtig geheugen toepassing ontwikkeld en gekarakteriseerd. Nadat deze delicate diëlektrica zijn gevormd worden ze dikwijls tijdens de verdere processtappen blootgesteld aan een zeer agressieve omgeving. De mogelijke processchade tijdens deze verdere processtappen werd gekarakteriseerd en geëvalueerd. Waar noodzakelijk werden de processtappen aangepast om de processchade te minimaliseren. Beschermingsmethoden werden ontwikkeld en toegepast.

Hoofdstuk 2 beschrijft de ontwikkeling van een PECVD oxynitride laag ter vervanging van een siliciumnitride laag. De nieuwe laag laat toe de SiGe bij een veel hogere snelheid selectief te deponeren bij de fabricatie van een heterojunctie bipolaire transistor. De samenstelling van de oxynitride laag werd gekozen op basis van de SiGe depositieselectiviteit, de etssnelheid en de inwendige spanning van de laag. De depositie snelheid van de SiGe kon worden verhoogd met een factor 4 tot 5. Goed elektrisch gedrag en hoge opbrengst werden gedemonstreerd.

Een belangrijk probleem bij 'floating gate' gebaseerde niet-vluchtige geheugens zoals flash geheugens of EEPROMs is het abnormaal ladingsverlies dat leidt tot verlies van gegevens. In hoofdstuk 3 worden verscheidene types tunneloxides vergeleken en wordt hun invloed op het abnormaal ladingsverlies bestudeerd met verscheidene meettechnieken. Er wordt aangetoond dat een snelle  $Q_{\rm BD}$  test op het kanaal-tunnel oxide dezelfde kwaliteit-volgorde geeft als het abnormale ladingsverlies test voor nieuwe geheugencellen. De  $Q_{\rm BD}$  test op het junctietunneloxide geeft meer informatie over het gedrag van veel gebruikte geheugencellen. Tunnel oxide gegroeid met een nat oxidatieproces toont voor de beide gevallen de beste resultaten.

Deze delicate diëlektrica worden tijdens de verdere processtappen zeer gemakkelijk beschadigd. Plasma processen zijn de belangrijkste oorzaak van dit type beschadiging. Hoofdstuk 4 beschrijft de ontwikkeling van de teststructuren om de invloed te bepalen op transistoren, metaal-metaal capaciteiten en geheugencellen. Eveneens wordt de meest geschikte evaluatietechniek bepaald. Om plasma processchade te voorkomen dienen in de

meeste gevallen speciale beschermingsstructuren te worden gebruikt. Dit hoofdstuk biedt richtlijnen aan hoe en waar deze beschermingsstructuren te gebruiken.

In hoofdstuk 5 wordt dieper ingegaan op het mechanisme van de plasmaschade op gate- en tunneloxides. 'Electron shading' effecten worden besproken als functie van het transistor- en reactortype. Een nieuwe methode wordt voorgesteld om latente plasmaschade te bepalen aan de hand van meerlagige test structuren. Er wordt ook aangetoond in welke omstandigheden geheugencellen kunnen worden aangetast door plasmaschade. Geschikte beschermingsstructuren worden voorgesteld om plasmaschade te voorkomen. Tevens wordt het verband beschreven dat werd gevonden tussen 'gate' lek metingen en 'hot carrier' degradatie. Hiermee wordt aangetoond dat plasmaschade niet enkel de opbrengst beïnvloedt maar tevens de betrouwbaarheid van de IC's.

Hoofdstuk 6 toont aan dat niet enkel dunne gate oxides maar evenzeer oxides van meer dan 20nm zoals die worden gebruikt in metaal-metaal capaciteiten kunnen worden aangetast door plasmaschade. Ook hier worden geschikte beschermings-structuren voorgesteld om plasmaschade te voorkomen.

Tevens wordt aangetoond dat ook 'dikke' lagen diëlektrica onder de geschikte omstandigheden voldoende elektrische lading kunnen transporten om plasmaschade te induceren.

Hoofdstuk 7 beschrijft hoe na een stap-voor-stap evaluatie van een volledig CMOS proces, een aantal plasmaschade veroorzakende processtappen werden geïdentificeerd. Voor elk van deze gevallen werd het proces aangepast om de plasmaschade in voldoende mate te minimaliseren. Tevens werden grote defecten vastgesteld, veroorzaakt door een 'ESD'-achtige ontlading van metaal –metaal capaciteiten tijdens de verdere processtappen. Ook voor deze schade werd het mechanisme bepaald en werd de oorzaak verwijderd.

| 1. | Introduc | tion                                                            | 15 |

|----|----------|-----------------------------------------------------------------|----|

|    | 1.1      | Introduction                                                    | 15 |

|    | 1.2      | Bipolar Transistors                                             | 16 |

|    | 1.2.1    | Modern Silicon Bipolar Transistors                              | 16 |

|    | 1.2.2    | Self-Aligned Emitter and Base Contact                           | 17 |

|    | 1.2.3    | Polysilicon Emitter                                             |    |

|    | 1.2.4    | Sidewall Contact Process                                        | 18 |

|    | 1.2.5    | Epitaxial Base                                                  | 18 |

|    | 1.2.6    | Silicon-Based Heterojunction bipolar transistors                | 19 |

|    | 1.2.7    | SiGe Growth and HBT Fabrication                                 | 21 |

|    | 1.3      | Characterization of Tunnel oxides for flash memories            | 22 |

|    | 1.3.1    | Non-volatile memories                                           | 22 |

|    | 1.3.2    | Charge carrier transport through insulators                     | 23 |

|    | 1.3.3    | The HIMOS <sup>TM</sup> structure                               | 25 |

|    | 1.4      | Plasma damage                                                   | 26 |

|    | 1.4.1    | Plasma damage mechanisms                                        | 28 |

|    | 1.4.2    | Metal-insulator-metal capacitors                                | 30 |

|    | 1.4.3    | Evaluation and prevention of plasma damage                      | 31 |

|    | 1.4.4    | Impact of plasma damage on reliability                          | 32 |

|    | 1.5      | References                                                      | 33 |

| 2. | Oxynitri | ide development for selective epitaxy in HBTs                   | 39 |

|    | 2.1      | Process description.                                            | 40 |

|    | 2.2      | Goals for the oxynitride optimization                           |    |

|    | 2.3      | Selectivity of epitaxial deposition                             |    |

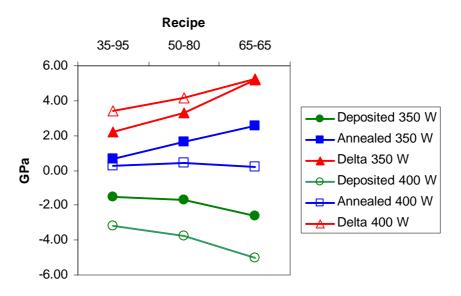

|    | 2.4      | Stress                                                          |    |

|    | 2.5      | Etch rate                                                       | 44 |

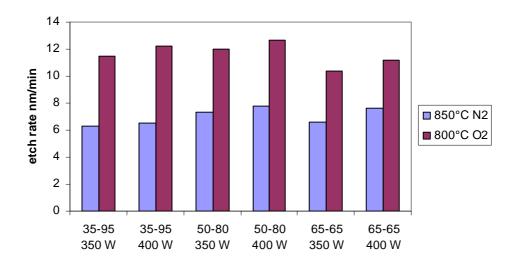

|    | 2.5.1    | Densification                                                   | 44 |

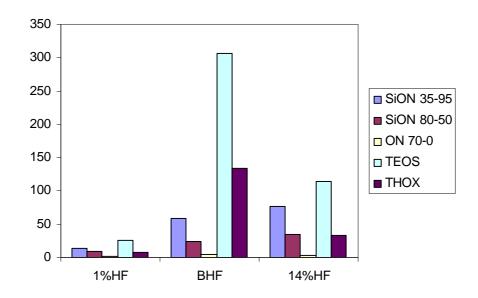

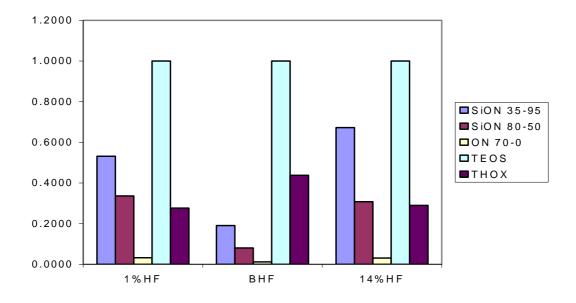

|    | 2.5.2    | Etchant vs. etch rate                                           | 45 |

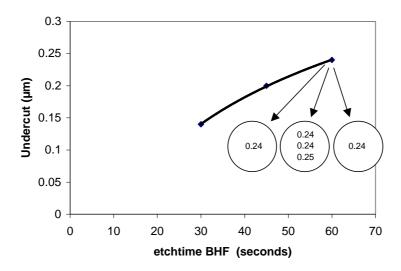

|    | 2.5.3    | Etch behaviour, uniformity and reproducibility                  | 47 |

|    | 2.5.4    | Cleaning and Particle performance                               |    |

|    | 2.6      | Thickness Uniformity                                            |    |

|    | 2.7      | Process window definition                                       | 49 |

|    | 2.8      | Performance and yield of the bipolar transistor                 | 50 |

|    | 2.9      | Conclusion                                                      | 51 |

|    | 2.10     | References                                                      | 51 |

| 3. | Characte | erization of tunnel oxides for non-volatile memory applications | 53 |

|    | 3.1      | Introduction                                                    | 53 |

|    | 3.2      | The experiment                                                  |    |

|    | 3.3      | The measurements                                                |    |

|    | 3.3.1    | Moving bits measurements                                        |    |

|    | 3.3.2    | Leakage measurements                                            |    |

|    | 3.3.3    | Q <sub>BD</sub> measurements                                    |    |

|    | 3.4      | Discussion                                                      |    |

|    | 3.5      | Conclusion                                                      |    |

|    | 3.6      | References                                                      |    |

|    |          |                                                                 |    |

| 4. |           | uctures, protection methods and evaluation methods for process damage                                                           | . 65 |

|----|-----------|---------------------------------------------------------------------------------------------------------------------------------|------|

|    | 4.1       | Introduction                                                                                                                    | 66   |

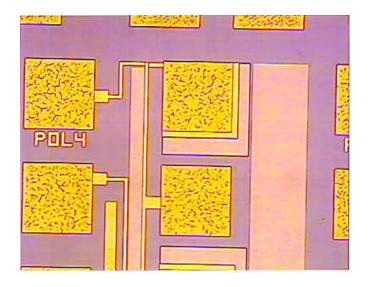

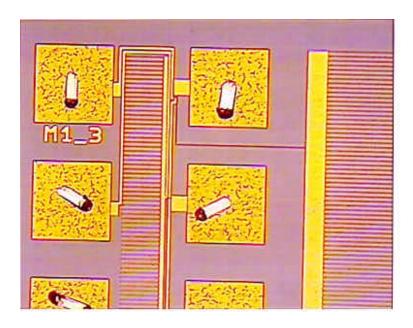

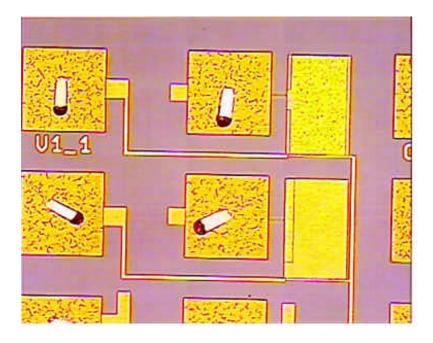

|    | 4.2       | Test structures                                                                                                                 | 68   |

|    | 4.2.1     | Concept of an antenna test structure                                                                                            | 68   |

|    | 4.2.2     | Standard set of MOS structures                                                                                                  | 69   |

|    | 4.2.3     | Specific MOS structures                                                                                                         | 74   |

|    | 4.2.4     | Specific metal-insulator-metal capacitor structures                                                                             | 75   |

|    | 4.2.5     | Specific Flash memory structures                                                                                                | 77   |

|    | 4.3       | Plasma process induced damage protection schemes                                                                                | 78   |

|    | 4.3.1     | Diode protection                                                                                                                | 78   |

|    | 4.3.2     | Capacitor protection                                                                                                            | 79   |

|    | 4.3.3     | Metal bridges                                                                                                                   |      |

|    | 4.4       | Evaluation techniques                                                                                                           |      |

|    | 4.4.1     | Surface charges                                                                                                                 |      |

|    | 4.4.2     | MOS Antenna structures                                                                                                          |      |

|    | 4.4.3     | Measurements on flash memory cells                                                                                              |      |

|    | 4.5       | Conclusion                                                                                                                      | 84   |

| 5. | Impact of | of plasma damage on gate and tunnel oxides                                                                                      | . 87 |

|    | 5.1       | Introduction                                                                                                                    | 88   |

|    | 5.2       | Impact of reactor- and transistor-type on electron shading effects                                                              | 89   |

|    | 5.3       | Plasma process-induced latent damage on gate oxide                                                                              | 93   |

|    | 5.5       | Correlation between hot carrier stress, oxide breakdown and gate leakage current.                                               | 100  |

|    | 5.6       | Conclusions                                                                                                                     | 104  |

|    | 5.7       | References                                                                                                                      |      |

| 6. | Impact of | of plasma and charging on thick (>20nm) dielectrics                                                                             | 107  |

|    | 6.1       | Introduction                                                                                                                    | 108  |

|    | 6.2       | Charging damage during Metal-Insulator-Metal capacitor manufacturing                                                            |      |

|    | 6.3       | Charging Induced damage by photoconduction through thick inter metal dielectrics                                                |      |

|    | 6.4       | Conclusion                                                                                                                      |      |

|    | 6.5       | References                                                                                                                      |      |

|    | 0.5       | References                                                                                                                      | 123  |

| 7. |           | cation, evaluation and optimization of critical process steps for induced damage                                                | 125  |

|    | •         | 6                                                                                                                               |      |

|    | 7.1       | Introduction                                                                                                                    | 126  |

|    | 7.2       | Optimization of high density plasma oxide deposition, Ar preclean and passivation processing in sub-half micron CMOS processing | 127  |

|    | 7.2.1     | Introduction                                                                                                                    |      |

|    | 7.2.2     | High density plasma inter metal dielectric oxide deposition                                                                     |      |

|    | 7.2.3     | Ar-preclean processing                                                                                                          |      |

|    | 7.2.4     | Pad opening etching: reactive ion etch vs. downstream                                                                           | 133  |

|    | 7.3       | Charging induced damage by water rinsing                                                                                        | 134  |

|    | 7.4       | Conclusion                                                                                                                      |      |

|    | 7.5       | References                                                                                                                      | 143  |

|    |           |                                                                                                                                 |      |

# **Chapter 1**

#### Introduction

#### 1.1 Introduction

Silicon dioxide is one of the most commonly encountered substances both in daily life and in electronics manufacturing. Beach sand is mostly silicon dioxide. The whole of planar electronics processing and the modern IC industry has been made possible by the unique properties of silicon dioxide: the only native oxide of a common semiconductor which is stable in water and at elevated temperatures, an excellent electrical insulator, a good dielectric, a mask to common diffusing species and capable of forming a nearly perfect electrical interface with its substrate. Deposited silicon dioxide, mostly manufactured by chemical vapour deposition, is almost as old as thermal growth on the substrate, and has been employed in various ways in IC fabrication due to its familiarity, versatility and reliability. Silicon dioxide has the wonderful ability to have its chemical, physical and electrical properties changed and moulded over a wide range according to the way it has been processed.

Therefore silicon dioxide has a premium role in the semiconductor industry for a very wide range of applications such as dielectric, insulator, topographical component and even as substrate for subsequent process steps. Over the various chapters, this thesis describes the characterization and development of a number of applications of silicon dioxides.

Once the oxide has been formed and defined it is exposed to the sometimes harsh environments during the following processing steps. It is a challenge to keep the delicate oxides intact all through the processing of the IC. Possible process damage due to this exposure is characterized, evaluation methods are developed, process steps are analysed for damage and protection methods are developed.

In this thesis, various aspects of dielectric engineering are considered. Chapter 2 describes the development of a PECVD oxynitride layer as a replacement for the nitride layer to allow a much higher growth rate of selective epitaxy in the heterojunction bipolar transistor. In chapter 3 we compare various types of tunnel oxides and determine the impact on anomalous charge loss with various measurement techniques. The delicate dielectrics are easily damaged during the further processing of the device. Plasma processing is a major source of process induced damage. Chapter 4 is describing the test and protection structures required for evaluation and prevention of plasma damage on MOS and metal-insulator-metal capacitors and HIMOS<sup>TM</sup> flash memory cells devices. In chapter 5, the in depth investigation of the effects of plasma damage on gate oxide and tunnel oxides are described. Chapter 6 describes the effects of plasma damage on thick (>20nm) dielectrics. And finally, chapter 7 describes how after a step-by-step investigation of a conventional 5 metal layer CMOS process, a number of plasma damage inducing process steps have been identified and eliminated. For each of these subjects, some background will be given in the following paragraphs.

#### 1.2 Bipolar Transistors

The bipolar transistor, one of the most important semiconductor devices, was invented by a research team at Bell Laboratories in 1947. It has had an unprecedented impact on the electronics industry in general and on solid-state research in particular. Prior to 1947 semiconductors were only used as thermistors, photodiodes and rectifiers. In 1948 John Bardeen and Walter Brattain announced the development of the point contact transistor [1]. In the following year William Shockley's classical paper on junction diodes and transistors was published [2].

Since then the transistor theory has been extended to include high-frequency, high-power and switching behaviour. Many breakthroughs have been made in transistor technology, particularly in the alloy-junction [3] and grown-junction techniques [4] and in zone-refining [5], diffusion [6], epitaxial [7], planar [8], beam-lead [9], ion implantation [10], lithography, and dry etching [11] technologies. These breakthroughs have helped to increase the power and frequency capabilities as well as the reliability of transistors. In addition, application of semiconductor physics, transistor theory and transistor technology has broadened our knowledge and improved other semiconductor devices as well.

Bipolar transistors are now key elements, for example, in high-speed computers, in vehicles and satellites, and in all modern communication and power systems. Many books have been written on bipolar transistor physics, design and application. Among them are standard texts by Philips [12] and Gartner [13] and a series of books by the Semiconductor Electronics Education Committee [14], Pritchard [15], Ghandhi [16], and Muller and Kamins [17].

#### 1.2.1 Modern Silicon Bipolar Transistors

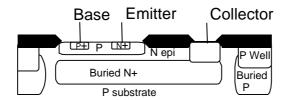

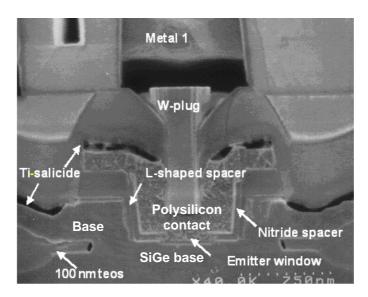

A representative for integrated silicon bipolar transistors is shown in Figure 1.1. Buried n+subcollectors are formed by implantation of arsenic or antimony into a p substrate, followed by epitaxial growth of highly doped silicon to form the collector layer. This is followed by isolation steps based on localized oxidation of the surface.

Figure 1.1:A representative for integrated silicon bipolar transistors.

The emitter is formed with the implantation of arsenic or phosphorus followed by base formation with boron ion implantation. Collector contact "plugs" may then be implanted. The structure is completed with the deposition of several layers of interconnect metal, separated by interlevel dielectric.

In recent years, advances have been made in the fabrication technology of silicon bipolar transistors, which have led to considerable reductions in vertical and lateral device dimensions, and corresponding increases in performance. This section discusses several of the common themes of present technology [18].

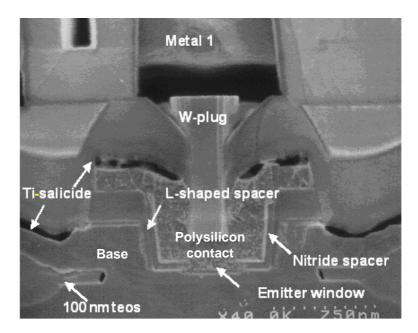

#### 1.2.2 Self-Aligned Emitter and Base Contact

Significant improvements over conventional technology are possible by employing emitters and extrinsic bases diffused from polysilicon layers, which remain on the wafer forming the respective contacts. The polysilicon layers withstand high process temperatures and can be oxidized, so they lend themselves to a variety of sophisticated processing techniques. In particular, the separation between the emitter contact and the base contact can be self-aligned, using a dielectric sidewall spacer whose width can be accurately controlled in the range of several hundred nanometers. The width of the emitter is equal to the width of the opening in the base polysilicon (defined photolithographically) minus the sidewall dimensions. A representative device cross-section is shown in Figure 1.2. By repeated application of sidewall spacers, emitter widths down to 0.35 µm have been made, starting from 1 µm lithographic patterns. The emitter polysilicon can extend over a considerably wider region than the area of contact, reducing its series resistance. The base-collector junction area is kept at a minimum, typically three times the emitter area, even for the very narrow emitters. Dramatic savings in device area are made over non-self-aligned devices, which require wide separations between base and emitter to allow for photolithographic alignment tolerances [18].

#### 1.2.3 Polysilicon Emitter

The use of polysilicon to form the emitter contact has had a major impact on transistor current gain, and therefore on vertical scaling. The value of the current gain appropriate to polysilicon depends on detailed process conditions, particularly on the amount of SiO<sub>2</sub> at the interface between single crystal and polysilicon. The amount of SiO<sub>2</sub> is typically governed by an HF dip prior to deposition of polysilicon, the subsequent thermal treatment and exposure of the resultant "hydrogen-passivated" surface, and on heat treatments after polysilicon deposition (which tend to break up the oxide). It is necessary to produce devices with relatively well-controlled values of this thickness; if the oxide is too thick, the series resistance of the emitter contact becomes excessive; if it is too thin, the current gain suffers [18].

With polysilicon, thin emitters can be produced with acceptable current gain. Thin emitters limit hole storage, and allow thin base regions to be formed with adequate control and with higher base doping. An advantage of polysilicon from the processing standpoint stems from the fact that implants of the emitter dopant (As) are made into the polysilicon material, followed by a drive-in anneal. Therefore, implant damage is kept away from the single-crystal material and by appropriate control of the anneal, extremely shallow emitters can be reproduced.

The formation of the base regions is also a critical fabrication step. The conventional method of forming the base layer is by boron implantation prior to emitter deposition. However, boron atoms have a pronounced tendency to channel, giving rise to implant distributions with deep tails. Thus, very low implant energies must be used, with the result that base charge becomes very sensitive to emitter depth [18].

#### 1.2.4 Sidewall Contact Process

The sidewall base contact structure transistor makes innovative use of polysilicon contacts to achieve considerable improvement in device performance and to increase the possible circuit uses of the device. A sidewall base contact transistor is shown in Figure 1.2. Thick oxide layers separate the base polysilicon from the collector, so that extrinsic base collector capacitance is dramatically reduced. With appropriate doping profiles, a nearly identical geometry can be obtained for current flow downward from emitter to collector and upward from collector to emitter. High-quality upward transistors can be used in circuit applications to simplify layout [18].

#### 1.2.5 Epitaxial Base

To overcome the problems of base layer formation by ion implantation and allow thinner base regions with controlled doping profiles, epitaxial growth of the base with in situ doping has been explored. The epitaxial process can be configured so that deposition takes place only on exposed single-crystalline regions of the silicon substrate. Alternatively, deposition can be made all across the wafer surface, although in regions covered by silicon dioxide, the silicon deposits are polycrystalline. The control achieved during epitaxy permits thinner bases and higher cutoff frequency. It is critical, however, to control the thermal budget of processing subsequent to the base growth, so that the boron dopant does not diffuse excessively. This is a particular concern during the emitter implantation step [18].

Figure 1.2: The sidewall base contact structure transistor makes innovative use of polysilicon contacts to achieve considerable improvement in device performance and to increase the possible circuit uses of the device. Thick oxide layers separate the base polysilicon from the collector, so that extrinsic base collector capacitance is dramatically reduced. Epitaxial growth of the base with in situ doping is used to overcome the problems of base layer formation by ion implantation and allow thinner base regions with controlled doping profiles.

Although polysilicon emitters and advanced processing have allowed shallower emitters and thinner base layers to be produced, there are limits to the vertical scaling achievable.

- As the base is thinned, base resistance is increased unless doping is also increased. This limit can be counteracted to a considerable extent by making narrow emitters, so that the distance between base contact and centre of the emitter stripe is kept at a minimum.

- It is necessary to avoid base punch-through at reasonable operating voltages. This requires increasing values of base doping as the structure is scaled.

- For higher base doping charge storage in the emitter is increased, cutoff frequency is decreasing and current gain drops.

- As the collector doping is increased to limit collector transit time and allow increasing current density, the breakdown voltage associated with collector avalanching decreases.

#### 1.2.6 Silicon-Based Heterojunction bipolar transistors

The constraints on vertical scaling of bipolar transistors may be overcome if the semiconductor composition can be changed appropriately within the device. This has a critical effect on current gain. In conventional silicon transistors, considerable improvement in transistor performance can be obtained by intentionally changing the semiconductor composition. The ability to tailor this layer provides a powerful new degree of freedom in the design of bipolar devices.

The implementation of heterojunction approaches in bipolar devices was delayed for decades because of the technological problem of providing interfaces between dissimilar materials that were free from imperfections, either impurities or structural defects. Even at the present time, high-performance heterojunction bipolar transistors are limited to relatively few materials systems. The most explored systems are those involving semiconductors that have identical lattice constants (GaAlAs/GaAs and InGaAs/InAlAs/InP) and those that use thin layers that adapt to the lattice constant of the substrate (SiGe/Si) [18].

To obtain the benefits of heterojunctions combined with standard silicon bipolar technology, considerable efforts have been made to identify a suitable semiconductor to be used as base within silicon devices.

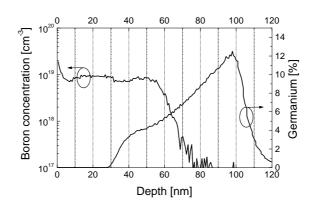

The pseudomorphic growth of a SiGe epitaxial layer results in compressive strain, low defect levels and improved electrical transport properties. By incorporating SiGe in a Si bipolar transistor the frequency limit of the devices is increased to the range normally associated with GaAs.

Experimental results have confirmed a variety of advantages of SiGe heterojunction bipolar transistors over transistors based on silicon alone, including:

- SiGe heterojunction bipolar transistors exhibit a nearly threefold improvement in cutoff frequency to over 130 GHz compared to silicon. Grading the Ge content of the base region also helps increase f<sub>T</sub> by providing a built-in field.

- Typical characteristics of SiGe and GaAs devices are quite comparable, GaAs having the superior f<sub>T</sub>; but SiGe enjoying lower noise parameters comparable to those of GaAs transistors.

- Early voltage increases with the use of germanium. The product of current gain and Early voltage is an important figure-of-merit for linear (analog) applications. Values of this figure-of-merit are increased by 20-100 times with the addition of germanium.

- By incorporating SiGe in a Si bipolar transistor, a higher base punch-through voltage is achieved.

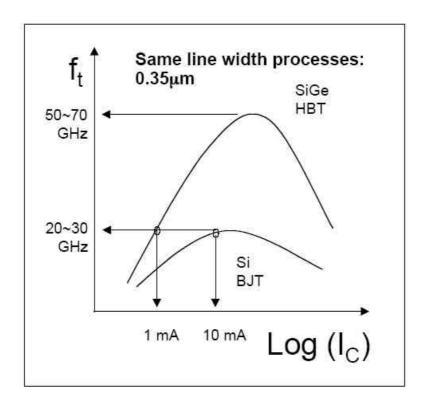

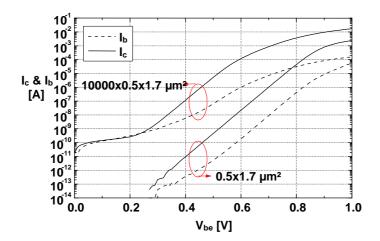

Figure 1.3: By maximizing the built-in field and reducing other delay components a significantly higher cutoff frequency  $f_T$ , up to 115 GHz, has been demonstrated. With respect to standard silicon bipolar devices, with identical processing, SiGe allows reduced current for equal performance.

The high-speed performance of SiGe heterojunction bipolar transistors is excellent. Figure 1.3 illustrates the advantage obtainable in  $f_T$  with respect to standard silicon bipolar devices with identical processing. By maximizing the built-in field and reducing other delay components, significantly higher  $f_T$ , up to 115 GHz, has been demonstrated [18].

#### 1.2.7 SiGe Growth and HBT Fabrication

Techniques for the growth of SiGe include molecular beam epitaxy, with either solid or gaseous sources; limited reaction processing, in which epitaxy is carried out from the vapour phase on a controlled basis using heating by high intensity lamps; and ultrahigh vacuum chemical vapour deposition, among others. A key feature in the ultrahigh vacuum chemical vapour deposition technique is the virtual elimination of oxygen, which allows growth to take place at lower temperatures than in ordinary silicon growth. This technique can provide uniform growth over multiple wafers.

Several possibilities exist for the growth of the SiGe for the base. Conditions can be chosen for:

- Non-selective growth, in which SiGe is deposited everywhere (although it will be polycrystalline when covering oxide or nitride layers). After the base deposition, the SiGe is covered with polysilicon to form the emitter.

- Selective growth of the SiGe so that it will deposit only in windows opened to silicon dioxide or silicon nitride films.

Etching is an important step in the fabrication of SiGe devices and circuits. Chemical etching of SiGe is in general similar to the etching of silicon, but presents quite some challenges. Device oxides can be prepared on SiGe. SiGe alloys with Ge content below 50% can be dry oxidized for MOS devices. Ge segregation occurs at the interface causing an unacceptable level of interface states.

For these reasons a choice was made for selective growth. With this technique, epitaxial silicon is deposited only in areas with exposed silicon. The remaining area of the wafer is covered with a suitable dielectric.

So far, interpoly dielectric layer, isolating the polybase from the subsequent poly-emitter, consisted of silicon nitride. This layer withstands the wet etch during further processing, but shows a limited selectivity during the epitaxial deposition. To maintain sufficient selectivity, the deposition rate of the epitaxial layer has to be kept very low. This is done introducing a high flow of HCl in the gas chemistry. In addition, the nitride layer has often to be used in combination with an extra underlying oxide layer [3]. The factors mentioned above have a severe negative impact on manufacturability and processing cost. Chapter 2 describes the use of a PECVD oxynitride layer instead of the nitride layer to allow a much higher deposition rate of the epitaxial layer. It describes the development, properties and implementation of the oxynitride into the HBT interpoly dielectric layer module of a SiGe BiCMOS technology [18].

#### 1.3 Characterization of Tunnel oxides for flash memories

Chapter 3 of this thesis is dedicated to the development of a reliable tunnel dielectric layer which can be applied in solid state non-volatile memories as the Electrical Erasable Programmable Read Only Memories (EEPROMs). The improvement of the electrical properties of the tunnel oxide and the development of a fast method for evaluation was the main challenge of the research described in chapter 3 of this thesis. First an introduction will be given in the basic principles of non-volatile memories, which is followed by a brief description of the mechanisms that can be used to transport charge carriers through insulators.

#### 1.3.1 Non-volatile memories

Solid-state non-volatile memories can store information for a very long time without the need of a power supply. This is in contrast with volatile memories like DRAM and SRAM, which do need a non-interrupted power supply.

Non-volatile data storage can be performed optically or magnetically on disks or tapes. Although a lot of data can be stored, the power consumption is high during read, write and idle state and the speed is relatively low. Electrical data storage however has the advantage of operating without mechanical parts, leading to much shorter access times and therefore a higher performance. Erasable Programmable Read Only Memories (EPROM) device can be programmed by hot carrier injection into the floating gate and can be erased by ultraviolet light exposure. The programming and erasure can be carried out several times by the user [21]. However for erasing these memories have to be taken out of the system, which is a disadvantage. One Time Programmable (OTP) EPROMs are EPROMs without the UV transparent window in the package. As a result, OTP's cannot be erased and they can therefore be classified as PROM. By giving up reprogrammability, OTP can use cheaper and smaller packages [21]. The most advanced memory is the EEPROM or E²PROM. This type of memory can be programmed and erased electrically without removing the memory chip from the system.

Nowadays a very popular memory is the so called Flash EEPROM, in which a large number of cells is erased at the same time (block or page). This is in contrast with EEPROMs where every byte can be erased separately. The most important advantage of Flash FEEROM over EEPROM is that the cell size is considerably smaller and is even approaching the cell size of DRAM and EPROM. It is mainly because of this reduced cell size and therefore lower cost and the fact that flash EEPROMS can contain huge amounts of data, that flash EEPROMs are now the dominant type of non-volatile memory [22, 23, 24].

Most non-volatile memory cell concepts are based on a standard MOS transistor. For instance the threshold voltage can be altered electrically between a low and a high value to represent logic 1's and 0's. A first method is varying the threshold voltage by changing the amount of charge that is stored in the gate dielectric, so a floating gate is not required. An example of this type of memory is known as a Metal Nitride Oxide Silicon (MNOS) transistor [40]. Charge is stored in the traps at the interface of the oxide and the nitride layer. In 1967, Kangh and Sze [19] introduced the use of a MOS transistor with a so called floating gate, which is a polycrystalline silicon layer that is completely surrounded by an insulating dielectric. This floating gate is capacitively coupled to other parts of the device. A second gate is placed on top of the floating gate, in order to control the floating gate potential through capacitive coupling.

#### 1.3.2 Charge carrier transport through insulators

The floating gate is electrically completely isolated from the other terminals by a surrounding dielectric layer. Under normal operating conditions, no charge can flow to or from this gate, leading to a typical storage time of more than 10 years.

Charge stored on the floating gate causes a shift in the threshold voltage of the MOS transistor. The threshold voltage of the MOS transistor can be manipulated by injecting negative charge on the floating gate. This operation is known as programming. For n-channel MOS transistors it results in a higher threshold voltage, which is defined as a logic '0'. By removing the negative charge from the floating gate, which is known as erasure, the device returns to the lower threshold voltage state, defined as a logic '1'.

To change the amount of charge that is stored on the floating gate of an (E)EPROM, charge carriers have to be transported through the dielectric layer that surrounds the floating gate. Carriers can be transported through the insulator by two mechanisms. One mechanism is tunnelling. With the second mechanism, electrons can gain sufficient energy to surmount the barrier. The energy to surmount the barrier can be obtained by an electron through interaction with radiation, e.g. photons [29], Fowler-Nordheim tunnelling [20], channel hot electron injection [21-23] and substrate hot electron injection [24 - 28].

#### - UV Stimulated injection

With the energy, gained through interaction with ultraviolet (UV) radiation, the electron can cross the oxide barrier [29]. If electrons are accelerated in an electric field they gain kinetic energy. This energy can be lost by collisions with lattice atoms. However, if the mean free path, i.e. the average distance between subsequent collisions is long enough [24], they can have more energy than the thermal energy corresponding to the lattice temperature. These highly energetic electrons are then called "hot" [41] and some are able to surmount the barrier. Two hot electron injection techniques are described in literature: Charnel Hot Electron injection [22] and Substrate Hot Electron injection [25].

#### - Channel hot electron injection

Programming by channel hot electron injection is done by making use of the pinch-off region, where a high electric field is available [42] [43] so that the electrons are accelerated from the channel into the pinch-off region. A disadvantage of this method is that the electric field in the oxide under these conditions is not directed towards the floating gate, since both the floating gate and drain potentials are providing the pinch-off condition. Only a small fraction of the hot electrons are accelerated into the desired direction, which leads to a low programming efficiency. The first EEPROM device using channel hot electron injection was presented in 1973 [22].

A third gate can be used to change the direction of the electric field and to improve the efficiency significantly. This method is known as source side hot electron injection [44, 45, 46]. A disadvantage is that the additional gate enlarges the cell and makes it more complex. By using hot electron injection the gate oxide is locally stressed in a small area near the drain junction or the source side, which is also a disadvantage compared to the more homogeneous injection with lower current density, achieved by substrate hot electron injection.

#### - Substrate hot electron injection

Substrate hot electron injection does not stress oxides locally, since electron injection takes place over the whole gate area. The hot electrons are generated by a vertical electric field under the gate, which accelerates the electrons in the direction of the insulator. Therefore a much more efficient programming is possible. The electrons can be provided for example by a forward biased p-n junction [25]. This method has a low efficiency since only a limited fraction of injected electrons reaches the insulator. The efficiency has been improved by the development of the Vertical Injection Punch-through based MOS (VIPMOS) EEPROM, in which a buried injector underneath the floating gate acts as a very efficient source of electrons [26].

#### - Fowler-Nordheim tunnelling

A very important mechanism for charge carrier transport through insulating layers is Fowler-Nordheim tunnelling [20]. Electrons have a finite probability to tunnel through a potential barrier. The tunnelling probability is determined by the height and width of the potential barrier. By applying an electric field the width can be decreased, leading to electron tunnelling from the conduction band of a semiconductor through the oxide barrier into the conduction band of an insulator.

In addition to Fowler-Nordheim tunnelling a different mechanism becomes significant for dielectric layers with a thickness below 5 nm, which is known as direct tunnelling. In that case electrons can tunnel through the barrier without using the conduction band of the insulator. However, for non-volatile memories this process is not useful since such barriers do not isolate the floating gate sufficiently.

Fowler-Nordheim tunnelling is used to erase the floating gate transistor in the High Injection (efficiency) MOS (HIMOS<sup>TM</sup>) cell. It takes place from the floating gate to the drain of the MOS. The oxide layer in this overlap region can be processed as a special thin oxide, called tunnel oxide. Tunnelling in this oxide occurs when a sufficiently large potential difference is applied between the floating gate and the drain or source. When a potential difference is applied between the floating gate and the substrate, tunnelling will occur in the gate oxide. In this case the control gate will be used to bias the floating gate. The first EEPROM using tunnelling for write and erase was introduced by Intel which is the well known Flotox EEPROM [47].

Fowler-Nordheim tunnelling deteriorates the insulating properties of the tunnel oxide which may result in a malfunctioning of the memory device, i.e. stored charge may leak away (poor data retention) or the number of program/erase cycles is very low (poor endurance).

By applying these methods, currents are forced to flow through the dielectric layer, in this case gate oxide at high electric fields. This is rather contradictory since dielectric layers are primarily known for their good isolating properties. Therefore a lot of energy is put in the development of the dielectric layers in EEPROM devices, since the electrical behaviour of the devices is dominated by the insulating properties of these layers.

A lot of effort already has been put into improving the electrical properties of the interpoly dielectric layers in the last few decades: different types of oxide layer [30], stacks of oxide and/or nitride layers [31, 32] and different post deposition treatments [30, 33] have been investigated in order to improve the reliability of the memory cells. The improvement of the electrical properties of the tunnel oxide and the development of a fast method for evaluation was the main challenge of the research described in chapter 3 of this thesis.

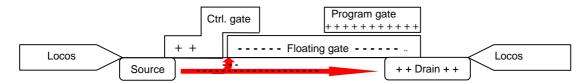

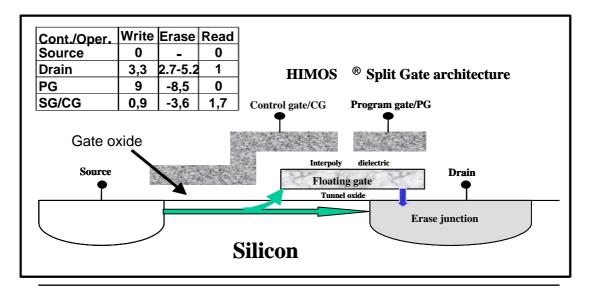

# 1.3.3 The HIMOS<sup>TM</sup> structure

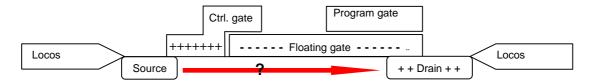

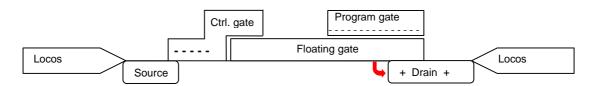

The HIMOS<sup>TM</sup> structure is depicted under three different operating conditions: writing (A), reading (B) and erasing (C). The arrows indicate the direction of movement of the electrons.

1.4.A: During writing the MOS between source and drain is operated in a hot carrier regime by a limited voltage on the control gate. A high voltage is applied to the program gate to collect electrons in the floating gate.

1.4.B: During reading the MOS is partially switched on by the control gate. Depending on the charges collected in the floating gate, electrons are flowing to the drain.

1.4.C: During erasure a strong negative voltage is applied to the program gate. Due to this field the electrons collected in the floating gate are tunnelled to the drain.

The voltages necessary for operating the memory cell are listed in table 1.1.

|             | Write | Erase        | Read |

|-------------|-------|--------------|------|

| Source      | 0V    | =            | 0V   |

| Drain       | 3.3V  | 2.7V -> 5.2V | 1V   |

| Prog. gate  | 9V    | -8.5V        | 0V   |

| Contr. Gate | 0.9V  | -3.6V        | 1.7V |

Table 1.1: Terminal voltages for operating the memory cell of figure A, B and C.

Besides the concepts in which only single HIMOS<sup>TM</sup> structures are used, this structure is also applicable in large memory arrays. Arranging the cells in an array gives the possibility to share terminals of cells and to connect many cells by the same wires. In this manner, the total chip area can be reduced. The source/injector terminals can be shared by the cells next to each other. The erase gates are connected to each other; therefore a complete row of cells is erased at the same time. The effective size of every cell is  $135 \, \mu m^2$ .

During writing and especially during erasing, a current is forced through the tunnel oxide in between the substrate and the floating gate. This degrades the insulating properties of the tunnel oxide. When the tunnel oxide is degraded too far, charges leak away from the floating gate to the substrate. This anomalous charge loss leads to threshold voltage shifts on a time scale of months or years at room temperature. We refer to the bits showing such low-temperature long-term  $V_t$  shifts as anomalous SILC or moving bits. The number of moving bits is greatly affected by the nature and properties of the tunnel oxide that is used in the non-volatile memory technology. Chapter 3 compares different types of tunnel oxides and determines the impact on the moving bit issue. Together with the impact of the different types of oxide, different measurement methods are compared and evaluated.

#### 1.4 Plasma damage

Besides the formation of a dielectric meeting all the required specifications of performance and reliability, it is a major challenge to keep this dielectric intact throughout the full manufacturing process of the integrated circuit. Especially for gate oxides, a major issue is the use of plasma processing during the manufacturing process. The plasma process ambient is a very harsh environment which influences the yield and reliability of finished semiconductor devices.

In the 50 years since the invention of transistor silicon integrated circuit technology has made astonishing advances. A key factor that makes these advances possible is the ability to have precise control on material properties and physical dimensions. The introduction of plasma processing in pattern transfer and in thin film deposition is critical for enabling further downscaling in the semiconductor technology. In state of the art silicon integrated circuit manufacturing process, plasma is used in more than 20 different critical steps.

Plasma is sometimes called the fourth state of matter (other than gas, liquid and solid). It is a mixture of ions (positive and negative), electrons and neutrals in a quasi-neutral gaseous steady state, sustained by an energy source that balances the loss of charged particles. It is a very harsh environment for the delicate integrated circuits. Highly energetic particles such as ions, electrons and photons bombard the surface of the wafer continuously. These bombardments can cause all kinds of damage to the silicon devices that make up the integrated circuit.

Very early on in the introduction of plasma processing in silicon IC manufacturing, people became aware of the potential danger due to plasma damage to the devices. Much effort had been devoted to understand the damage mechanisms and to find ways to avoid or fix them. There is a huge body of literature on the subject. Most of the damage studies focused on physical damage to crystalline silicon by energetic ions and electrical damage to  $SiO_2$  and its interface by energetic photons.

More recently a different kind of plasma damage has become important. This is charging damage. The first reported observation of plasma charging damage was in 1984 [63]. A high electric field apparently developed across the gate-oxide of a metal-oxide-semiconductor-field-effect transistor during plasma processing. This high electric field leads to gate-oxide breakdown or wear out (lifetime shortening). It was quite unclear at first how such an electric field could develop.

In more recent years, plasma process induced damage has become a major industry-wide problem requiring an interdisciplinary approach. In modern VLSI manufacturing extremely tight control on every production step is required. Plasma processing steps are no exception. Plasma processing tools have been developed at great expense to achieve excellent uniformity across the wafer. Gone are old tools such as the barrel etcher with poor plasma uniformity. Yet, in modern IC manufacturing plasma charging damage is more prevalent: the reason for this increase in incidence of damage is due mostly to the continued scaling down of gateoxide thickness. As with many other problems in the integrated circuit industry, the impact of plasma process induced damage on real products has been aggravated by the relentless scaling of device and interconnect dimensions. Currently, interconnecting 10<sup>7</sup>-10<sup>8</sup> transistors constitutes a major technological challenge requiring the use of multi-level metallization schemes. To achieve this goal, high density plasma enhanced deposition and etching techniques have to be used. However, the use of high density plasma reactors and the accompanying higher density of charging species (10<sup>12</sup> ions/cm<sup>3</sup>) impose a major yield and reliability threat. This negative effect is further aggravated by the use of ever thinner gate oxides. The combination of high-density plasmas and thinner gate oxides therefore constitutes one of the major threats for the operational lifetime of integrated circuits [48] [49]. A thinner gate-oxide requires a lower voltage to support Fowler-Nordheim tunnelling: it is more vulnerable to plasma non-uniformity.

On the other hand, if one were to calculate the plasma potential variation across the wafer based on the measured ion current or etch rate in most modern plasma processing tools, one would have found that the voltage variations are often lower than what is needed to cause damage. Clearly the actual floating potential variation across the wafer must be higher than what is suggested from these measurements. It is, of course, quite possible that the measurement method is inadequate and that the real variation in plasma potential is larger. Still, apart from plasma non-uniformity, other mechanisms generating plasma damage should be considered. These other possibilities will be explored in chapter 4, 5 and 6 of this work.

#### 1.4.1 Plasma damage mechanisms

The three main plasma process induced damage models are based on surface charging, the non-uniformity of the plasma and on the electron shading effect [50].

#### - Surface charging

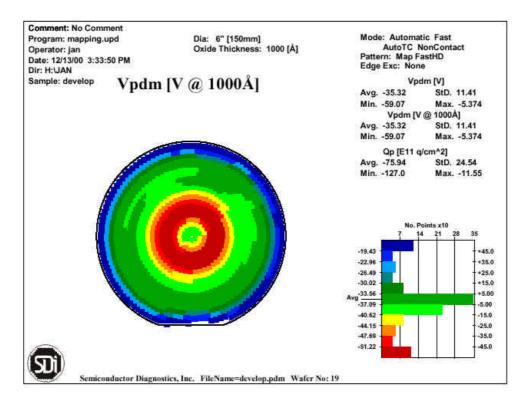

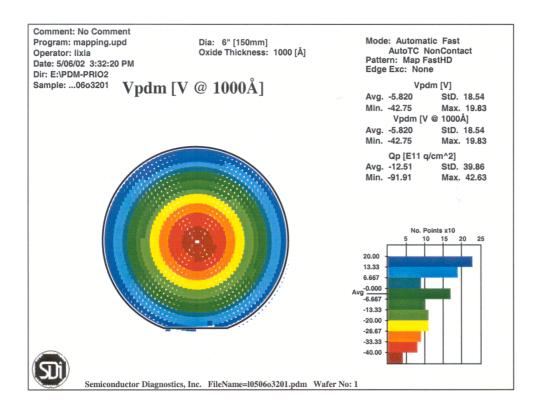

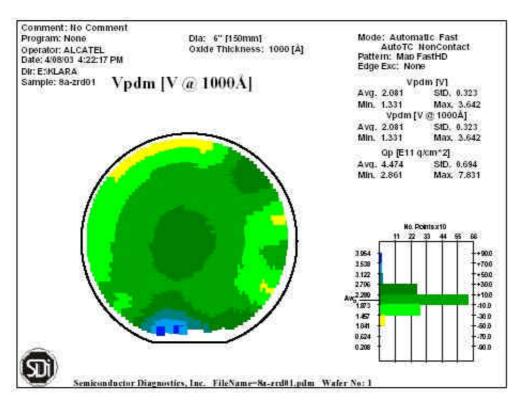

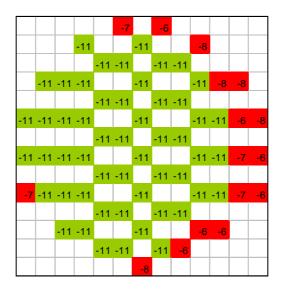

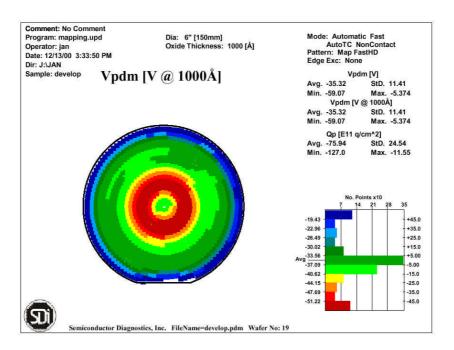

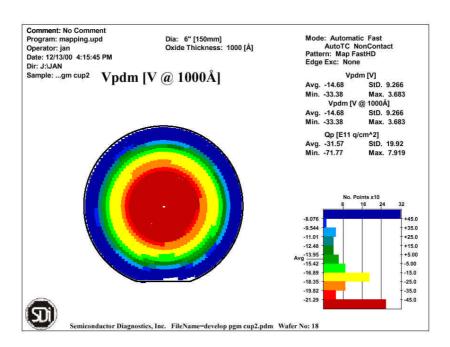

Some processes are capable of generating a considerable quantity of charges on a surface. These charges can be generated simply by friction. Under the right conditions, the charging of a surface can also be the effect of a plasma. Figure 1.5 shows the mapping of the charges collected on a wafer surface by a high speed water spray on the centre of a silicon oxide wafer surface. When the silicon substrate is grounded, the full electric field is distributed over the thin oxide. When the electric field exceeds the field that the oxide can support, a destructive Fowler-Nordheim current starts to flow through the oxide.

Similarly, voltages built up by friction can easily reach the range of several thousands of volts and can be very destructive. These phenomena are grouped under the name electrostatic discharge.

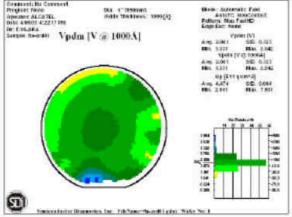

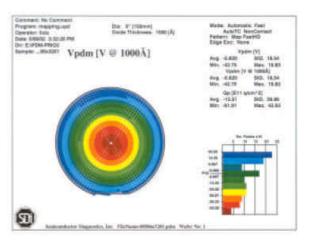

Figure 1.5: For mapping of the charges collected on a wafer surface, a plasma damage monitoring tool manufactured by Semiconductor Diagnostics Inc. was used. This technique measures the build-up of the deposited plasma charges during plasma processing on top of an unpatterned SiO<sub>2</sub> film. In this example a high speed water spray generated –59 V charging in the centre ring of the wafer.

#### - Plasma non-uniformity

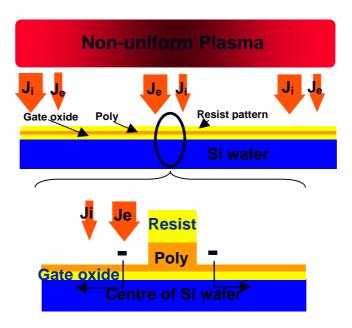

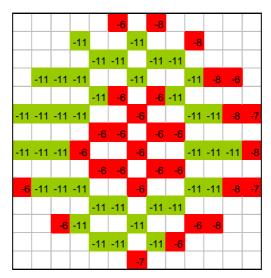

Non-uniform plasma discharge causes a local imbalance in ion and electron currents on the wafer surface. The edges of a wafer surface can be charged opposite compared to the charging in the centre surface of the wafer. The bulk of the wafer is conductive and can support the current required for balancing the non-uniform charging of the wafer surface.

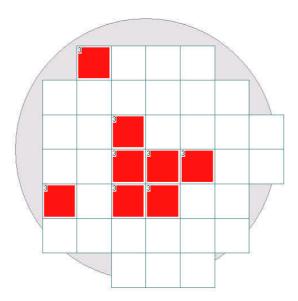

When etching a conductive pattern connected to a gate oxide, the charging of the conductor continues until the maximum field is reached that can be supported by the thin gate oxide connected to the conductive layer. When the electric field is high enough, destructive Fowler-Nordheim current starts to flow through the oxide as depicted in Figure 1.6.

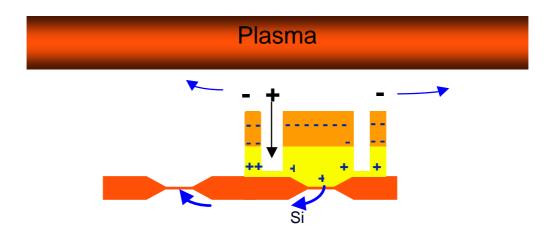

Figure 1.6 Non-uniform plasma discharge causes a local imbalance in ion and electron currents. The top picture shows a plasma inducing more negative charges by a negative electron current  $J_e$  in the centre of a wafer. The edges of the wafer are objected to a positive ion current  $J_i$ . The bottom picture shows how due the dominating negative electron current, the wafer centre is charged negatively and an electric field builds op over the gate oxide. Plasma damage occurs once the field built up over the gate oxide exceeds the voltage that can be supported by the gate oxide. At that moment a FN current (depicted by the arrows) flows through gate oxide and induces damage.

#### - Electron shading

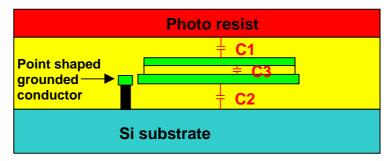

Even in uniform plasmas charging can occur. Most important is the electron shading effect in which negative charges on the photoresist prevent electrons from penetrating into the trenches being etched. As depicted in figure 1.7 this causes positive charging of the gate electrode in case of high aspect ratio patterns even for perfectly uniform plasmas [50],[51]. This phenomenon occurs for any etch/ash with insulator over conductor as is the case during poly or metal patterning.

Figure 1.7 When an antenna has a dense resist pattern, the resist charges negatively and "shades" electrons from entering the antenna. This is causing positive charging of the conductor: electrons are deflected by the negative charge built up in the resist as depicted by the top arrows. Mainly positive ions can still reach the conductor through the trenches in the resist. The positive charged conductor induces an electric field over the gate oxide: a FN tunnelling current starts to flow through the gate oxide (as depicted by the bottom arrows) and plasma damage is occurring.

#### 1.4.2 Metal-insulator-metal capacitors

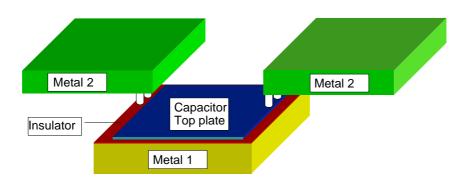

Apart from the increasing use of high density plasmas in combination with very thin gate oxides, CMOS devices are being extended to RF applications, for the fast expanding field of telecommunications. Typical for the BiCMOS-RF technologies is the use of inductors in combination with capacitors. High performance mixed signal and RF circuits require integrated capacitors with low voltage coefficients, good capacitor matching, precision control of capacitor values and low parasitic capacitance along with high reliability and low defect density. Conventional high-density capacitors such as poly-substrate, see for example [52], poly-poly, see for example [53] and metal-poly [54] [55] structures suffer from high voltage coefficients due to voltage induced depletion effects as well as higher parasitic capacitance due to their proximity to the substrate. Metal-insulator-metal (MIM) capacitors

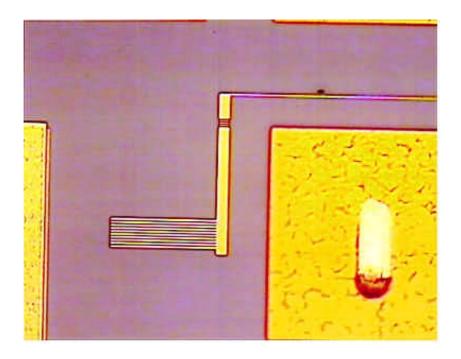

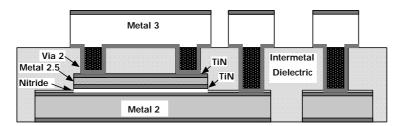

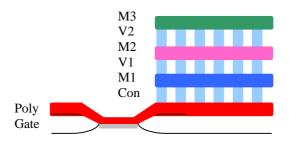

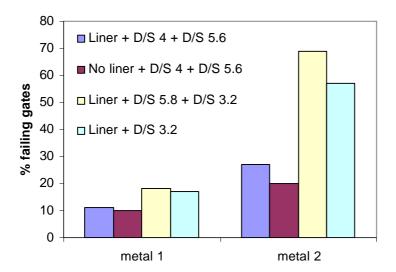

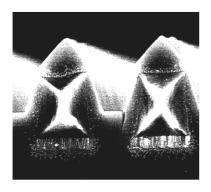

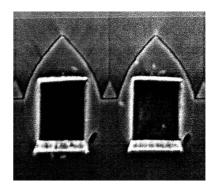

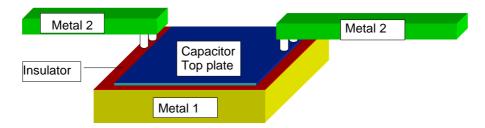

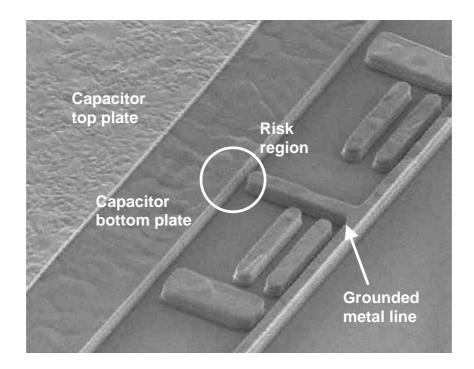

have low parasitic capacitance, especially when fabricated on metal 2 or higher, as well as high quality factor for RF circuit applications [56]. High-density metal-insulator-metal capacitors with capacitance densities of 1.0 to 2.0 fF/µm² using PECVD nitride dielectric have been integrated into the backend metallization layers of a CMOS or BiCMOS process flow. Capacitor breakdown voltage, linearity and reliability meet mixed-signal circuit requirements. Less than 0.5 defects/cm² has been achieved for 2.0 fF/µm² capacitance density. A quality factor larger than 10 at 1 and 2GHz was measured indicating its usefulness in RF applications. As depicted in figure 1.8 these capacitors are made as metal-insulator-metal capacitors. The application of the thin dielectric together with the metal processing in a high density plasma environment makes these metal-insulator-metal capacitors very vulnerable to plasma damage [56]. In this thesis, special attention is paid to the mechanisms on how plasma damage affects these devices and how they can be protected.

Figure 1.8. BiCMOS RF technologies use inductors in combination with capacitors. These capacitors are made as metal-insulator-metal capacitors.

#### 1.4.3 Evaluation and prevention of plasma damage

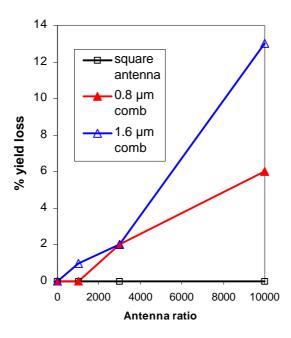

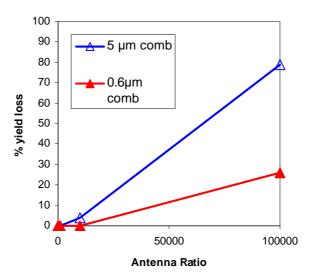

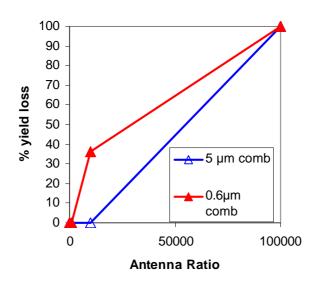

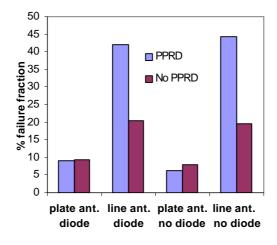

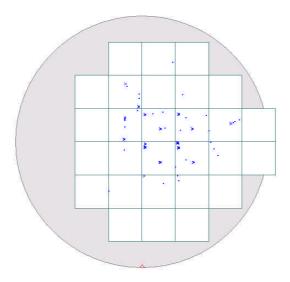

To evaluate the plasma process induced damage caused by the different process modules on gate oxides and metal-insulator-metal capacitors, test structures with large antennas connected to the gate electrode have been developed. Typically, large plate and comb antennas are used for the poly and metal patterning processes whereas antennas with a large number of contact and via holes are used to assess the plasma process induced damage introduced during contact and via processing. Besides that, electron shading effects are studied by varying the spacing of the comb antennas. However, also more dedicated test structures have been designed to achieve a better understanding of the more fundamental plasma process induced damage aspects, such as timing and pattern density related aspects [57] [58]. Chapter 4 of this work describes the test structures required for evaluation of plasma damage on MOS and metal-insulator-metal capacitors. As a special case of CMOS, test structures are developed to investigate the impact of plasma damage on HIMOS TM flash memory cells.

To assess the impact of topography, evaluation methods are required that allow qualification of processes in an efficient but reliable way using the antenna structures. Chapter 4 of this work compares evaluation techniques such as voltage breakdown, charge pumping, gate

leakage and threshold voltage measurements. The measurement methods are compared in terms of sensitivity, speed and ease of use.

Non-contact surface charge measurements provide a fast and indirect way to detect plasma process induced damage. This type of measurement is typically used to monitor the plasma (non-) uniformity by measuring the surface charge on non-patterned oxide wafers. After the plasma process, the potential on the oxide surface can be measured by means of a plasma damage monitoring tool (Semiconductor Diagnostics Inc.). The absolute potential (Vpdm) and the potential difference ( $\Delta$ Vpdm) reflect the potential charging contribution of final stages of the deposition process. This technique, however, does not detect electron shading effects [59]. In chapter 5 the application of this measurement in order to detect possible sources of plasma damage is described.

In the majority of cases, however, protection structures need to be foreseen already in the design phase of the circuit [60]. Chapter 5 provides design guidelines, possible scenarios and required limitations for protecting semiconductor devices against plasma damage. In other cases, plasma damage can be prevented by the development of the proper process. Chapter 6 describes how process optimization can lead to plasma damage reduction.

#### 1.4.4 Impact of plasma damage on reliability

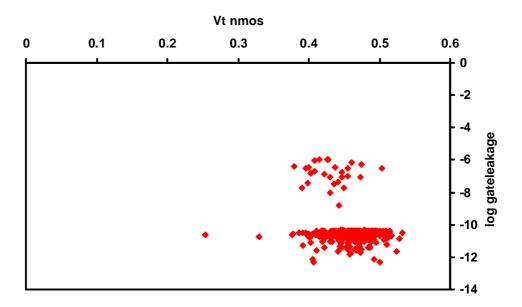

Apart from the impact on the gate oxides, plasma damage can have impact on other reliability parameters. In chapter 7 of this work it is the intention to correlate two reliability parameters: hot-carrier degradation behaviour and breakdown of the gate oxide to the accumulated damage during plasma processing.

Hot-carrier stress typically occurs under high silicon and relatively low oxide field conditions. In the technologies that are considered here, the dominant degradation mechanism is interface trap generation in NMOS and electron trapping in PMOS [61]. This is clearly different from the high-field oxide degradation case where the dominant degradation mechanism finally leading to oxide breakdown is bulk trap generation [62]. The higher density of bulk oxide electron traps in devices that suffered from plasma charging damage might influence the trapping behaviour under hot-carrier stress conditions. For this reason it is worthwhile to investigate if and to what extent hot-carrier degradation rate is influenced by the accumulated damage during plasma processing.

If a clear correlation could be found between gate leakage and both HC degradation and oxide breakdown, it would prove that plasma damage affects not only yield but also reliability and lifetime of the devices. On top it would suggest that gate leakage current can be used to monitor device reliability under plasma stress, thereby saving a lot of measurement time and prevent possible reliability problems in the field.

#### 1.5 References

- [1] J. Bardeen and W. H Brattain, "The Transistor, A Semiconductor Triode", Phys. Rev., 74, 230, 1948.

- [2] W. Shockley, "The Theory of p-n Junctions in Semiconductors and p-n Junction Transistors", Bell Syst. Tech. J., 28, 435, 1949.

- [3] R.N. Hall and W. C. Dunap, "p-n Junctions Prepared by Impurity Diffusion", Phys. Rev., 80, 467, 1950.

- [4] G.K. Teal, M. Sparks, and E. Buehlor, "Growth of Germanium Single Crystals Containing p-n Junctions", Phys. Rev., 81, 637, 1951.

- [5] W.H. Pfann, "Principles of Zone-Refining", Trans. AIME, 194, 747, 1952.

- [6] M. Tanenbaum and D. E. Thomas, "Diffused Emitter and Base silicon Transistor", Bell Syst. Tech. J., 35, 1, 1956.

- [7] H.C. Theuerer, J. L Kleimack, H. H. Loar, and H. Christenson, "Epitaxial Diffused Transistors", Proc. IRE, 48, 1642, 1960.

- [8] J.A. Hoerni, "Planar Silicon Transistor and Diodes", IRE Electron Devices Meet., Washington D.C., 1960.

- [9] M.P. Lepselter, "Beam-Lead Technology", Bell Syst. Tech. J., 45, 233, 1966.

- [10] W. Shockley, U.S. Patent 2,787,564 (1954), For a view on ion implantation, see J. F. Gibbons, "Ion Implantation in Semiconductors-Part 1, Range Distribution Theory and Experiments", Proc. IEEE, 56, 295, 1968.

- [11] E.F. Labuda and J.T. C1emens, "Integrated Circuit Technology", in R. E. Kirk and D. F. Othmer, Eds., Encyclopedia of Chemical Technology, Wiley, New York, 1980.

- [12] A.B. Phillips, Transistor Engineering, McGraw-Hill, New York, 1962.

- [13] W.W. Gartner, Transistors, Principle, Design and Application, D. Van Nostrand, Princeton, N.J., 1960.

- [14] SEEC (Semiconductor Electronics Education Committee), 4 vols.

- (1) R.B. Adler, A.C. Smith, and R.L. Longini, Introduction to Semiconductor Physics, SEEC Vol. 1, Wiley, New York, 1966.

- (2) P.E. Gray, D. DeWitt, A.R. Boothroyd and E.P. Gibbons, Physical Electronics and Circuit Models of Transistors, SEEC Vol. 2, Wiley, New York, 1966.

- (3) C.L. Searle, A.R. Boothroyd, E.J. Angelo, P.E. Gray, and D.G. Pederson, Elementary Circuit Properties of transistors, SEEC, Vol. 3, Wiley, New York, 1966.

- (4) R.D. Thornton, D. DeWitt, E.R. Chenette, and P.E. Gray, Characteristics and Limitations of Transistors, SEEC, Vol. 4, Wiley, New York, 1966.

- [15] R. L. Pritchard, Electrical Characteristics of Transistors, McGraw-Hill, New York, 1967.

- [16] S.K. Ghandhi, Semiconductor Power Devices, Wiley, New York, 1977.

- [17] R.S. Muller and T.I. Kamins, Device Electronics for integrated Circuits, Wiley, New York, 1977.

- [18] S.M. Sze, Modern Semiconductor Device Physics, Wiley, New York 1998.

- [19] D. Kangh and S.M. Sze, "A floating gate and its application to memory devices", in Bell Syst. Tech. J., Vol. 46, pp. 1238, 1967.

- [20] M. Lenzlinger, E. H. Snow, "Fowler-Nordheim tunnelling into thermally grown SiO<sub>2</sub>", Journal of Applied Physics, Vol. 40, No. 1, pp. 278-283, 1969.

- [21] C.N. Berglund, R.J. Powell, "Photoinjection into Si0<sub>2</sub>:Eletctron Scattering in the Image Force Potential Well", Journal of Applied Physics, Vol. 42, No. 2, pp. 573-579, 1971.

- [22] H.C. Card and A.G. Worall, "Reversible floating-gate memory", Journal of Applied Physics, Vol. 44, No. 5, pp. 2326-2330, 1973.

- [23] G. Perlegos, S. Pathak, A. Renninger, W. Johnson, M. Holler, I. Skupnak, M. Reitsma, C. Kuhn, "A 64K EPROM using scaled MOS Technology", ISSCC Technical Digest, pp. 142-143, 1980.

- [24] T.H. Ning, C.M. Osburn, H.N. Yu, "Emission Probability of Hot Electrons from Silicon into Silicon Dioxide", Journal of Applied Physics Vol. 48, No. 1, pp. 286-293, 1977.

- [25] B. Eitan, J.L. McCreary, D. Amrany, J. Shappir, "Substrate Hot-electron EPROM", IEEE Transaction on Electron Devices Vol. 31, No. 7, pp. 934-942, 1984.

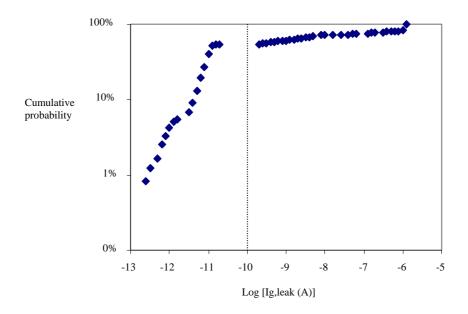

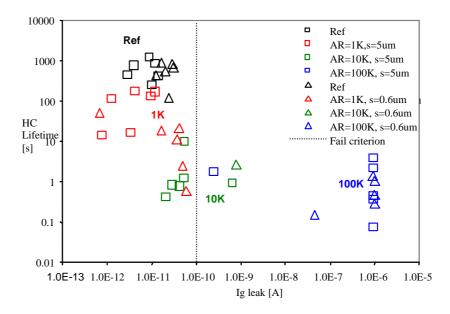

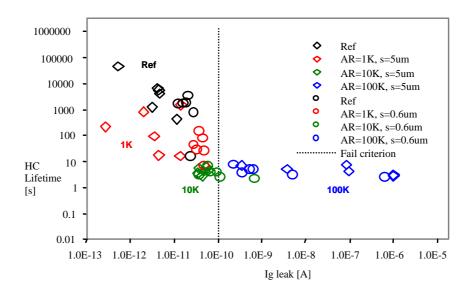

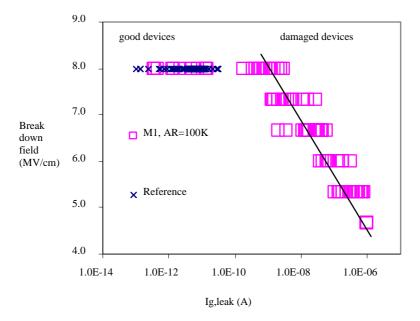

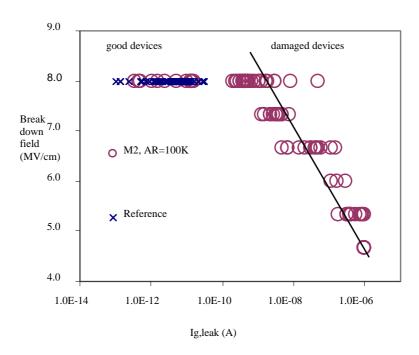

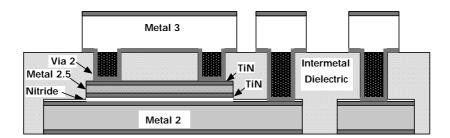

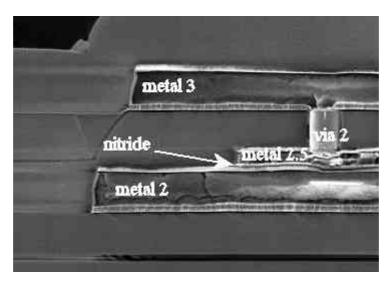

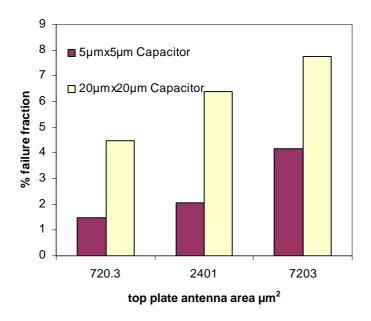

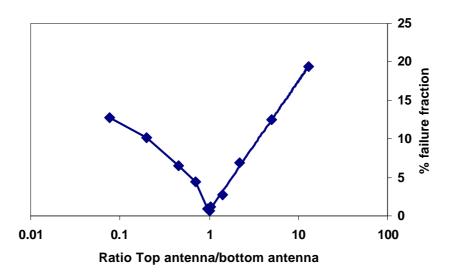

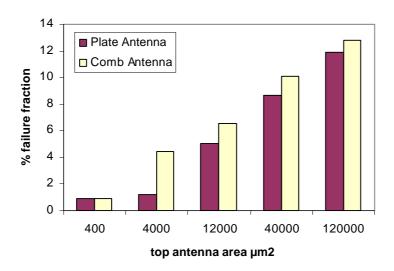

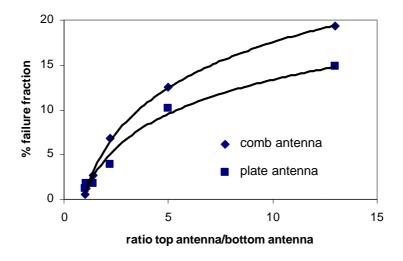

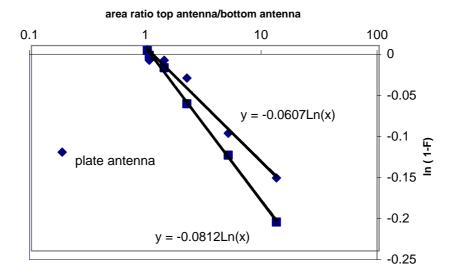

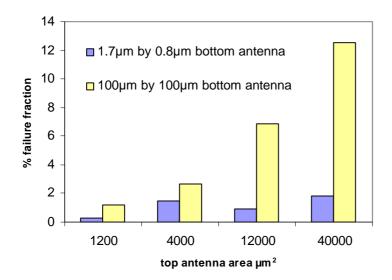

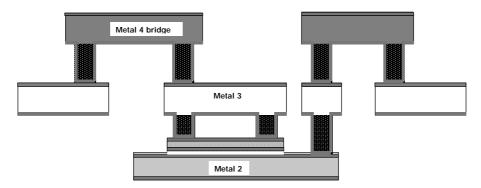

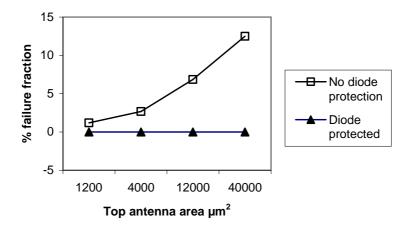

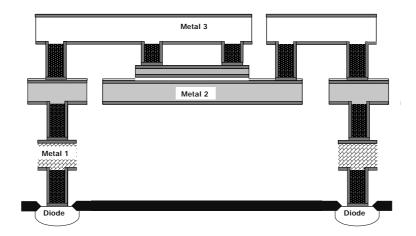

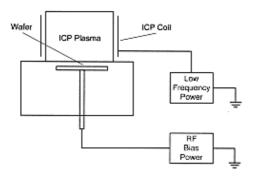

- [26] R.C. M. Wijburg, G.J. Hemink, J. Middelhoek, H. Wallinga and T.J. Mouthaan, "VIPMOS a novel buried injector structure for EPROM applications", IEEE Transactions on Electron Devices, Vol. 38, No. 1, pp. 111-120, 1991.